## **LED Co negative driving IC**

#### **Overview**

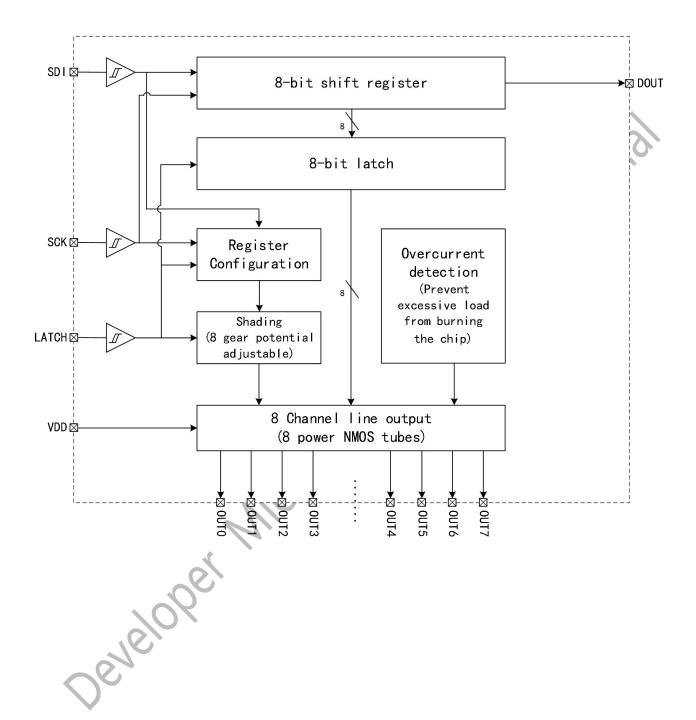

DP32029C is a serial decoding common cathode driver chip designed specifically for LED scanning screens. Integrated 8-channel NMOS row switch circuit, with high-performance adaptive shadow cancellation, LED bead short circuit and open circuit series lighting processing functions. Integrating a serial decoding circuit that prevents multiple channels from simultaneously opening can prevent the burning of the chip due to excessive channel current caused by the simultaneous opening of three or more channels. DP32029C can completely replace the original 3-8 decoder (74HC138) circuit of LED modules, effectively simplifying the complexity of LED module PCB wiring and improving the overall image effect of the display screen.

#### 2 Characteristics

- working voltage 3.0V~5.5V

- Integrated multi-channel to prevent simultaneous activation of serial decoding circuit

- Support arbitrary scanning

- Integrated 8-channel power NMOS transistor

- $OUT_MAX = 2.5A @ VDD = 5.0V$

- $RON=80m\Omega@VDD=5.0V\&IOUT=1.0A$

- Maximum power consumption < 600 mW @ VDD = 5.0V

- Integrated anti ghosting adaptive function, effectively eliminating line dragging shadows

- The erasing potential can be configured with registers to adapt to more

#### environments

- Improve the display cross line phenomenon caused by LED open circuit

- Simplify the complexity of LED module PCB wiring

- Packaging form:SOP16, QFN4\*4-16L

- Excellent ESD characteristics

### 3 Application areas

- High refresh rate LED video display

- Single color dual color full-color LED display

- High density and small spacing LED light board display

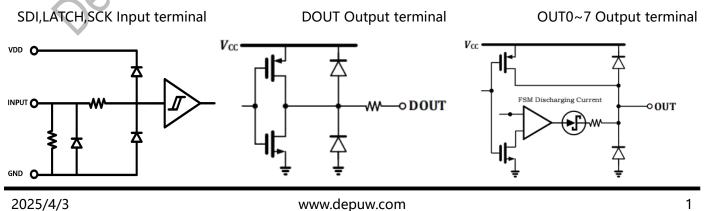

## 4 Circuit schematic diagram

### 4.1 Internal Circuit Block Diagram

DP32029C REV1.4 EN

### 4.2 Internal Circuit Block Diagram

2025/4/3 www.depuw.com 2

DP32029C REV1.4 EN

# Directory

| 1 Overview                                                                      | 1  |

|---------------------------------------------------------------------------------|----|

| 2 Characteristics                                                               | 1  |

| 3 Application areas                                                             | 1  |

| 4 Circuit schematic diagram                                                     | 1  |

| 4.1 Internal Circuit Block Diagram                                              | 1  |

| 4.2 Internal Circuit Block Diagram                                              |    |

| 5 Product Description                                                           | 5  |

| 6 Suggestions for Applying Circuits                                             | 7  |

| 7 Parameter Table                                                               | 8  |

| 7.1 Maximum limit parameters                                                    | 8  |

| 7.2 Recommended scope of work                                                   | c  |

| 7.3 DC Electrical Characteristics (VDD=5.0V)                                    | 9  |

| 7.4 Dynamic Characteristics (Unless otherwise specified, VDD=3.5V~5V, Ta=25 °C) |    |

| 8 Timing waveform diagram                                                       |    |

| 9 Row switch Control and blanking Time                                          |    |

| 10 Configuration register                                                       |    |

| 11 Package size                                                                 |    |

| The delage size                                                                 | 17 |

## **Revision History**

| version                                           | Revision<br>date | Revised by | Revision content                                     |  |  |

|---------------------------------------------------|------------------|------------|------------------------------------------------------|--|--|

| V1.0                                              | 2023.12          | WM         | 1.Initial version                                    |  |  |

| V1.1                                              | 2024.03          | WM         | 1. Modify the number of scans supported              |  |  |

|                                                   |                  |            | 2. Modify the equivalent circuit of input and output |  |  |

| V1.2                                              | 2025.02          | WM         | 1. Modify the QFN4*4-16L Package information         |  |  |

| V1.3                                              | 2025.03          | WM         | 1. Modify Row switch control                         |  |  |

| \/1 /                                             | 2025.04          | \A/\       | 2. Modify the configuration register                 |  |  |

| V1.4                                              | 2025.04          | WM         | I. Modify the Package Information                    |  |  |

| V1.4 2025.04 WM 1. Modify the Package information |                  |            |                                                      |  |  |

# **5 Product Description**

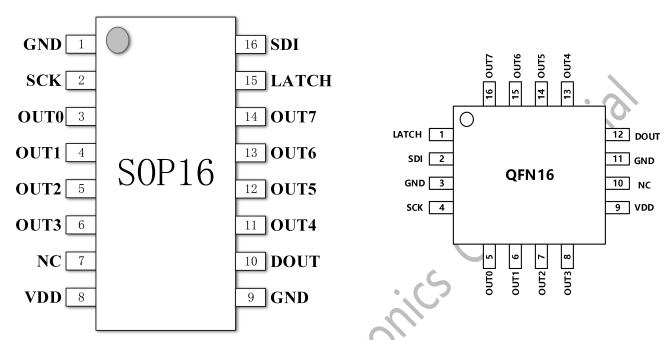

#### Pin definition

SOP16 Pin Definition Diagram

QFN4\*4-16L Pin Definition Diagram

#### Pin description

| SOP16 Pin | QFN4*4-16L Pin | Pin Name  | pinouts                                     |

|-----------|----------------|-----------|---------------------------------------------|

| number    | number         |           |                                             |

| 8         | 9              | VDD       | power input                                 |

| 16        | 2              | SDI       | data input                                  |

| 15        | 1              | LATCH     | Serial signal clock input                   |

| 2         | 4              | SCK       | Configure clock input for blanking register |

|           |                | 3CK       | configuration                               |

| 3~6, 4~7  | 5~8, 13~16     | OUT0~OUT7 | OUT output                                  |

| 1,9       | 11             | GND       | grounds                                     |

| 10        | 12             | DOUT      | serial data output                          |

| 7         | 10             | NC        | Empty foot                                  |

#### Product ordering information

| product name               | Packaging form | Packaging method | Quantity/Plate | Humidity          |

|----------------------------|----------------|------------------|----------------|-------------------|

|                            |                |                  |                | sensitivity level |

| <b>D D D D D D D D D D</b> | SOP16          | braid            | 4000           |                   |

| DP32029C                   | QFN4*4-16L     | braid            | 5000           | MSL=3             |

2025/4/3 DP32029C REV1.4 EN

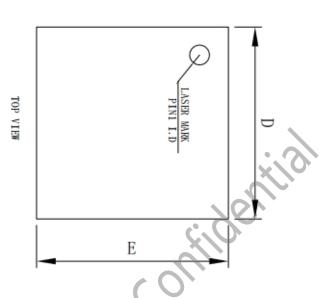

#### **Product labeling**

SOP16

**DP32029C**

QFN4\*4-16L

Developer Microelectronics

Oeveloper DP32029C is the product name XXXXXX represents the product batch number

2025/4/3 DP32029C REV1.4 EN

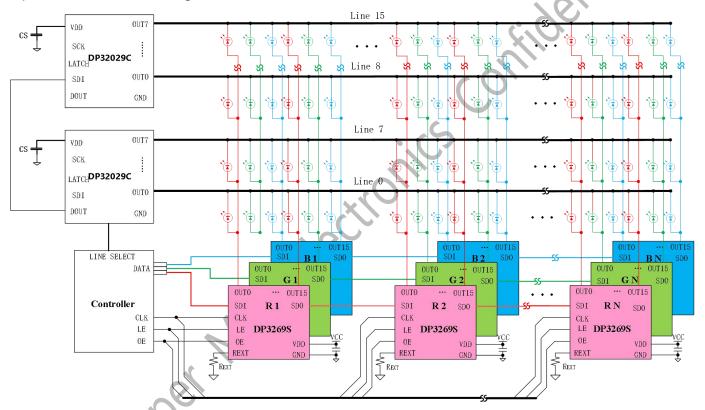

### **6 Suggestions for Applying Circuits**

Due to the widespread use of LED scanning screens in indoor display screens to reduce costs, the parasitic capacitance of the LED anode can instantly generate a discharge path during scanning switching, causing the display screen to experience ghosting; Users can use the DP32029C with discharge circuit function and refer to the recommended application circuit for the scanning screen shown in the figure below, and pair it with the built-in constant current driver chip DP5125 with pre charging function, which can completely eliminate the up and down ghosting phenomenon.

Due to the fact that DP32029C is an 8-channel output integrated power chip, to avoid excessive heat accumulation, it is recommended to use it on display screens with 16 or more scans, and pay attention to the temperature conditions during use.

LED Display Screen 16 Scan Application Block Diagram

### 7 Parameter Table

### 7.1 Maximum limit parameters

| project                                  | symbol      | Rated Value  | unit |

|------------------------------------------|-------------|--------------|------|

| supply voltage                           | <b>V</b> cc | 0~6.0        | V    |

| Input voltage (all pins)                 | Vin         | -0.4~VDD+0.4 | V    |

| Continuous working current at OUT end    | lo          | -2.5         | Α    |

| Instantaneous maximum current at OUT end | lout_max    | -3.5         | А    |

| power loss                               | PD          | <600         | mW   |

| Encapsulation thermal resistance         | Rth(j-a)    | 80           | °C/W |

| operation temperature                    | Topr        | -40~85       | °C   |

| storage temperature                      | Tstg        | -40~150      | °C   |

| HBM Human Body Model                     | Vesd        | ≥8           | KV   |

- All voltage values are based on the chip ground terminal (GND) as the reference point, and the maximum limit parameter test temperature is 25 °C.

- If the actual working conditions exceed the specified values, it may cause permanent damage to the components; If the actual working conditions are slightly lower than the maximum value and work for a long time, it may reduce the reliability of the components. The above are only partial specified values, and this product does not support functional operations under conditions other than specifications.

- The maximum peak welding temperature of surface mounted products cannot exceed 260 °C, and the temperature curve should be set by the factory according to the J-STD-020 standard, reference to the actual situation of the factory, and recommendations from the solder paste manufacturer.

Denelo

# 7.2 Recommended scope of work

| project                | symbol          | Test conditions                        | minimu<br>m<br>value | Typical values | Maxim<br>um<br>value | unit |

|------------------------|-----------------|----------------------------------------|----------------------|----------------|----------------------|------|

| supply voltage         | V <sub>cc</sub> | -                                      | 3.5                  | 5.0            | 5.5                  | V    |

| Output voltage(DOUT)   | $V_{DOUT}$      | -                                      | 0.7                  | -              | V <sub>DD</sub>      | V    |

| Output surrent/DOLIT   | I <sub>OH</sub> | V <sub>OH</sub> =V <sub>DD</sub> -0.5V | -                    | -16            |                      | mA   |

| Output current(DOUT)   | I <sub>OL</sub> | V <sub>OL</sub> =0.5V                  | -                    | 20             | -                    |      |

| input                  | V <sub>IH</sub> | V -2.2V F.FV                           | 0.7 V <sub>DD</sub>  | -              | $V_{DD}$             | V    |

| voltage(SDI,LATCH,SCK) | $V_{IL}$        | V <sub>DD</sub> =3.3V~5.5V             | 0                    | -              | 0.3V <sub>DD</sub>   | V    |

# 7.3 DC Electrical Characteristics (VDD=5.0V)

| project                            | symbol                    | Test conditions                                 | minimu<br>m<br>value | Typical values | Maxim<br>um<br>value | unit |

|------------------------------------|---------------------------|-------------------------------------------------|----------------------|----------------|----------------------|------|

| Logic power supply voltage         | V <sub>DD</sub>           | - 0                                             | 3.0                  | 5.0            | 5.5                  | V    |

| Power supply<br>current            | I <sub>DD_OFF</sub>       | All OUT outputs are set to low                  | ı                    | 400            | -                    | uA   |

| Gate opening voltage               | V <sub>GS(th)</sub>       | $V_{DS}=V_{GS}$ , $I_D=250uA$                   | ı                    | -0.7           | -0.9                 | V    |

| Source drain conduction resistance | R <sub>DS</sub> (on)[1:7] | V <sub>GS</sub> =-5.0V, I <sub>OUT</sub> =-1.0A | -                    | 80             | 120                  | mΩ   |

| high<br>input level                | V <sub>IH</sub>           | Logic potential                                 | 0.7 V <sub>DD</sub>  | -              | $V_{DD}$             |      |

| voltage Low<br>Level               | V <sub>IL</sub>           | Logic potential                                 | 0                    | -              | 0.3 V <sub>DD</sub>  | V    |

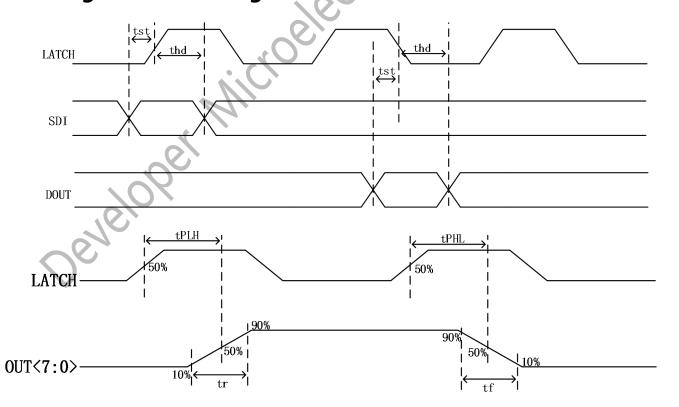

# 7.4 Dynamic Characteristics (Unless otherwise specified, VDD=3.5V~5V, Ta=25 °C)

| project              | symbol           | Test conditions | minimu<br>m<br>value | Typical values | Maxim<br>um<br>value | unit |

|----------------------|------------------|-----------------|----------------------|----------------|----------------------|------|

| Output rise delay    | t <sub>PLH</sub> |                 | -                    | 50             | -                    | ns   |

| Output descent delay | t <sub>pHL</sub> |                 | -                    | 100            | 410                  | ns   |

| Output rising edge   | t <sub>r</sub>   | VDD=5.0V        | -                    | 60             | -                    | ns   |

| Output falling edge  | t <sub>f</sub>   | CL=12pF         | 6                    | 400            | -                    | ns   |

| Establishment time   | t <sub>st</sub>  |                 | 60                   | -              | -                    | ns   |

| hold time            | t <sub>hd</sub>  |                 | 60                   | -              | -                    | ns   |

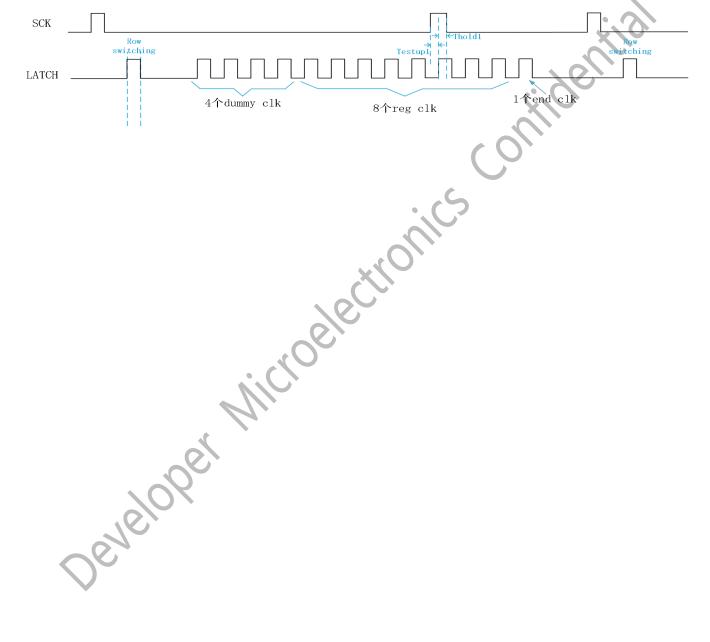

# 8 Timing waveform diagram

2025/4/3 DP32029C\_REV1.4\_EN

www.depuw.com

10

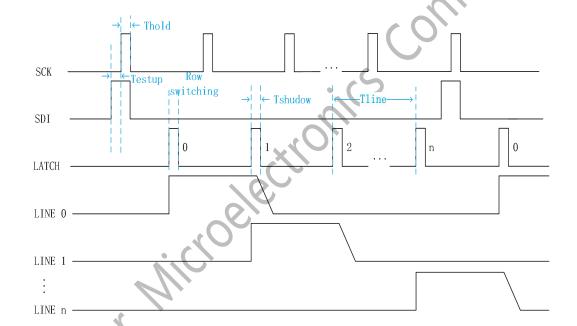

## 9 Row switch Control and blanking Time

DP32029C is a common cathode display serial decoder line tube driver, where each Row Switch is fixed to send 1 LATCH, and the channel output is high effective; the input data SDI to the output data DOUT is fixed to be at the rising edge interval of 8 SCK.

| Symbols | Description                               | Min value | Max value |

|---------|-------------------------------------------|-----------|-----------|

| Tshadow | Equal to LATCH signal high<br>level width | 500ns     | -         |

| Tsetup  | Setup time                                | 60ns      | 7-10      |

| Thold   | Hold time                                 | 60ns      | 76/1-     |

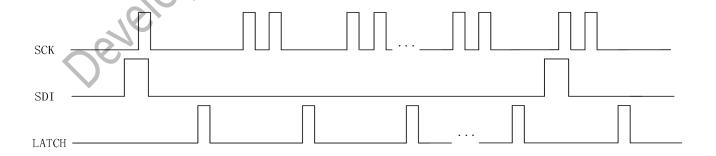

Scan the waveform line by line

Interlaced scanning configuration waveform

Number of rows =6 as an example:

Send 6 SCK impulses, only one SCK rising edge samples to SDI high level, others SCK rising edge is sampled to SDI low level, The time from the back to the front is recorded as the first, the second..6th SCK rising edge.If the NTH SCK rising edge is sampled to the SDI high level, Step 2 enable the display of the NTH channel.

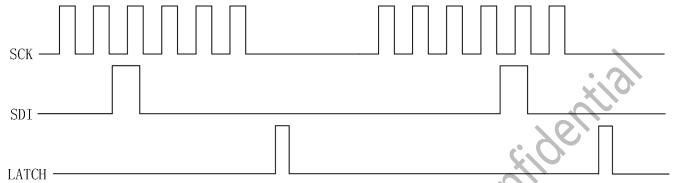

Configuration waveform for any scan

## 10 Configuration register

DP32029C Built in 4bit register:

| BIT | Name       | Default | Description                                                                                                                                                     |                                                                                                           |                                                                                                                                                                           |  |  |

|-----|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3   | VR_UP[2]   | 1′ b1   | Pull up the erasing circuit reference potential configuration register ,the highest bit n VR_UP[2:0]                                                            |                                                                                                           |                                                                                                                                                                           |  |  |

| 2   | reserved   | 1′ b0   | reserved                                                                                                                                                        |                                                                                                           |                                                                                                                                                                           |  |  |

| 1:0 | VR_UP[1:0] | 2' b10  | Pull up the cancellation circ<br>VR_UP[2:0] can be set to (V<br>0000: Vdd*7/20 =1.75V<br>0001: Vdd*8/20 =2.0V<br>0010: Vdd*9/20 =2.25V<br>0011: Vdd*10/20 =2.5V | 1000 : Vdd*11/20 = 2.75V<br>1001 : Vdd*12/20 = 3.0V<br>1010: Vdd*13/20 = 3.25V<br>1011 : Vdd*15/20 = 3.5V | Default 2.75V Data pin matching: SDI corresponds to c signal of 3-8 decoding; LATCH corresponds to A signal of 3-8 decoding; SCK corresponds to B signal of 3-8 decoding; |  |  |

| Symbol  | Description | Minimum value | Maximum value |

|---------|-------------|---------------|---------------|

| Tsetup1 | Setup time  | 60ns          | -             |

| Thold1  | Hold time   | 60ns          | -             |

2025/4/3 DP32029C\_REV1.4\_EN www.depuw.com

12

#### **Configuration Register mode:**

Register configuration is completed by two signals, SCK and LATCH, the configuration waveform is divided into three steps as shown below:

- (1)LATCH sends four dummy CLK pulses, and the chip enters register configuration after receiving them.

- (2)LATCH continues to send 8 CLK pulses, and the value of the sampled SCK of the NTH LATCH pulse is stored in the NTH bit of the register  $(N=1\sim8)$ .

- (3)LATCH continues to send one CLK pulse, which the chip receives and exits the register configuration state.

2025/4/3 www.depuw.com 13 DP32029C REV1.4 EN

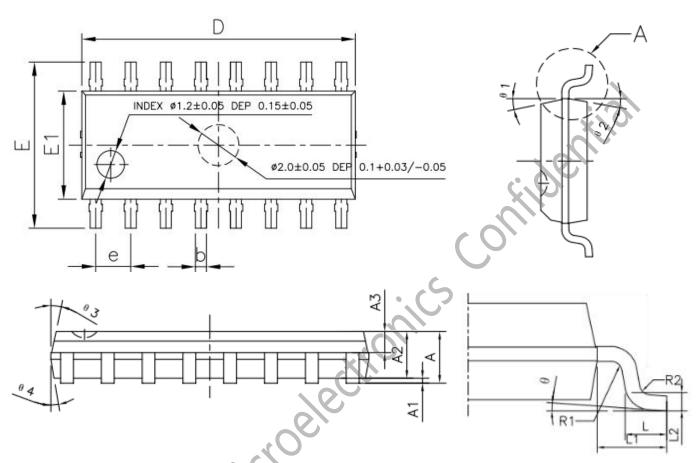

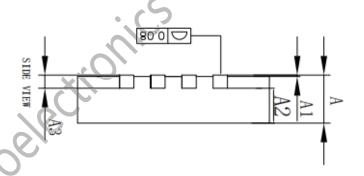

# 11 Package size

#### SOP16

| Symbol | Min     | Nom     | Max  |  |  |

|--------|---------|---------|------|--|--|

| Α      | -       | -       | 1.70 |  |  |

| A1     | 0.10    | 0.15    | 0.20 |  |  |

| A2     | 1.42    | 1.45    | 1.48 |  |  |

| A3     | 0.62    | 0.65    | 0.68 |  |  |

| b      | 0.38    | -       | 0.51 |  |  |

| D      | 9.85    | 9.90    | 9.95 |  |  |

| E      | 5.90    | 6.00    | 6.10 |  |  |

| E1     | 3.87    | 3.90    | 3.93 |  |  |

| е      | 1.24    | 1.27    | 1.30 |  |  |

| L      | 0.50    | 0.60    | 0.70 |  |  |

| L1     |         | 1.05REF |      |  |  |

| L2     |         | 0.25REF |      |  |  |

| Θ      | 0°      | -       | 8°   |  |  |

| Θ1-Θ4  |         | 12°REF  |      |  |  |

| R1     | 0.15REF |         |      |  |  |

| R2     |         | 0.15REF |      |  |  |

2025/4/3 DP32029C\_REV1.4\_EN

Densloy

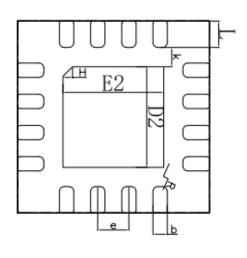

#### QFN4\*4-16L

|          | Symbol | Min      | Nom  | Max  |

|----------|--------|----------|------|------|

| Derielos | Α      | 0.70     | 0.75 | 0.80 |

|          | A1     | 0.00     | 0.02 | 0.05 |

|          | A2     | 0.5.     | 0.55 | 0.60 |

|          | A3     | 0.203REF |      |      |

|          | b      | 0.25     | 0.30 | 0.35 |

|          | D      | 3.90     | 4.00 | 4.10 |

|          | E      | 2.90     | 3.00 | 3.10 |

|          | D2     | 2.00     | 2.10 | 2.20 |

|          | E2     | 2.00     | 2.10 | 2.20 |

|          | Н      | 0.20REF  |      |      |

|          | K      | 0.40REF  |      |      |

|          | L      | 0.50     | 0.55 | 0.60 |

|          | е      | 0.65BSC  |      |      |

|          | R      | 0.09     |      |      |

#### 12 Official Announcement

Division I will ensure the accuracy and reliability of the product specification document, but we reserve the right to independently modify the content of the specification document without prior notice to the customer. Before placing an order, customers should contact us to obtain the latest relevant information and verify that this information is complete and up-to-date. All product sales are subject to the sales terms and conditions provided by our company at the time of order confirmation.

Division I will periodically update the content of this document. Actual product parameters may vary due to differences in models or other factors. This document does not serve as any express or implied guarantee or authorization.

The product specification does not include any authorization for the intellectual property owned by our company or any third party. With respect to the information contained in this product specification, we make no explicit or implied warranties, including but not limited to the accuracy of the specification, its fitness for commercial use, suitability for specific purposes, or non-infringement of our company's or any third party's intellectual property. We also do not assume any responsibility for any incidental or consequential losses related to this specification document and its use.

We do not assume any obligations regarding application assistance or customer product design. Customers are responsible for their own use of our company's products and applications. In order to minimize risks associated with customer products and applications, customers should provide thorough design and operational safety validation.

The reproduction, transmission or use of this document or its contents is not permitted without express written authority. Once discovered, the company will pursue its legal responsibility according to law and compensate for all losses caused to the company.

Please note that the product is used within the conditions described in this document, paying particular attention to the absolute maximum rating, operating voltage range, and electrical characteristics. The Company shall not be liable for any damage caused by malfunctions, accidents, etc. caused by the use of the product outside the conditions stated in this document.

Division I has been committed to improving the quality and reliability of products, but all semiconductor products have a certain probability of failure, which may lead to some personal accidents, fire accidents, etc. When designing products, pay full attention to redundancy design and adopt safety indicators, so as to avoid accidents.

When using our chips to produce products, Division I shall not be liable for any patent dispute arising from the use of the chip in the product, the specification of the product, or the country of import, etc., in the event of a patent dispute over the products including the chip.